|                 | Virtual and Physical Addresses                                                                                                                |                   |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

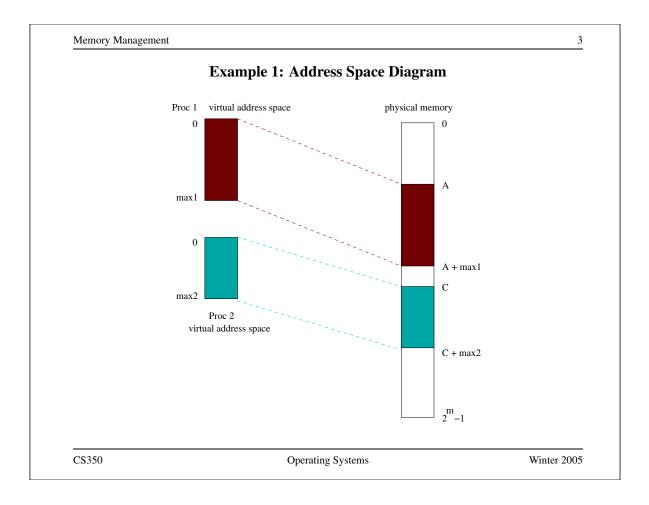

| • Physic        | cal addresses are provided directly by the machine.                                                                                           |                   |  |

| – on            | e physical address space per machine                                                                                                          |                   |  |

| of              | dresses typically range from 0 to some maximum, thou<br>this range are usually used by the OS and/or devices, a<br>ailable for user processes | 0 1               |  |

| • Virtua proces | al addresses (or logical addresses) are addresses provid sses.                                                                                | led by the OS to  |  |

| – on            | e virtual address space per process                                                                                                           |                   |  |

| – ad            | dresses typically start at zero, but not necessarily                                                                                          |                   |  |

| – sp            | ace may consist of several segments                                                                                                           |                   |  |

|                 | ess translation (or address binding) means mapping vir cal addresses.                                                                         | tual addresses to |  |

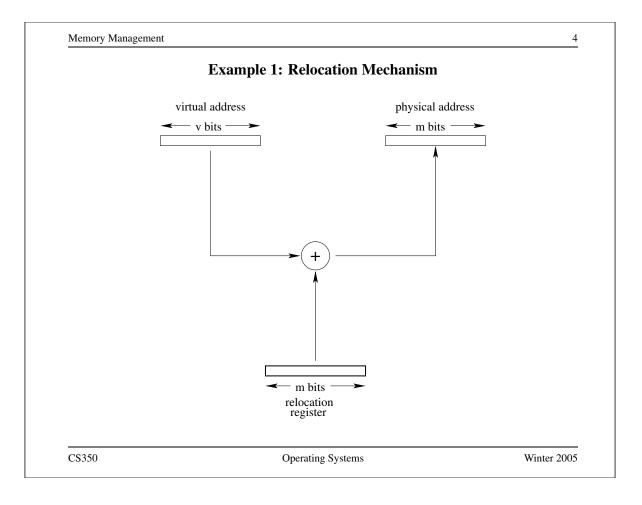

|                     | Example 1: Dynamic Relocation                                                                                                            |            |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| • hard <i>regis</i> | ware provides a <i>memory management unit</i> which includes a <i>rela</i><br>ter                                                        | ocation    |  |

|                     | <i>mic binding:</i> at run-time, the contents of the relocation register ch virtual address to determine the corresponding physical addr |            |  |

|                     | naintains a separate relocation register value for each process, as<br>res that relocation register is reset on each context switch      | nd         |  |

| • Prop              | erties                                                                                                                                   |            |  |

| <b>–</b> a          | ll programs can have address spaces that start with address $0$                                                                          |            |  |

| - (                 | S can relocate a process without changing the process's program                                                                          | m          |  |

|                     | S can allocate physical memory dynamically (physical partition hange over time), again without changing user programs                    | ns can     |  |

|                     | ach virtual address space still corresponds to a contiguous range hysical addresses                                                      | e of       |  |

| CS350               | Operating Systems                                                                                                                        | Winter 200 |  |

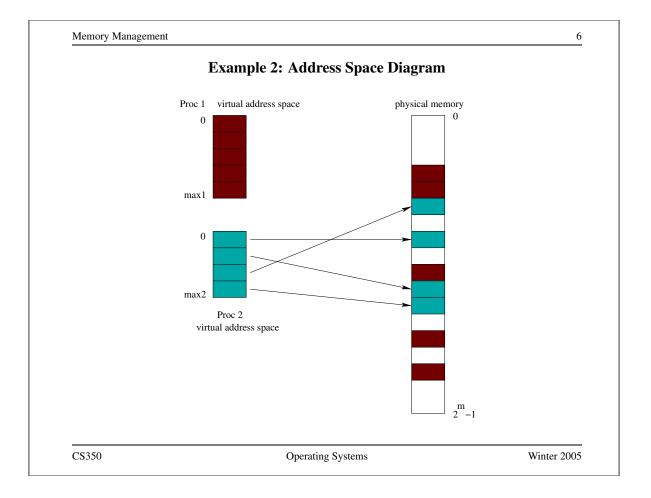

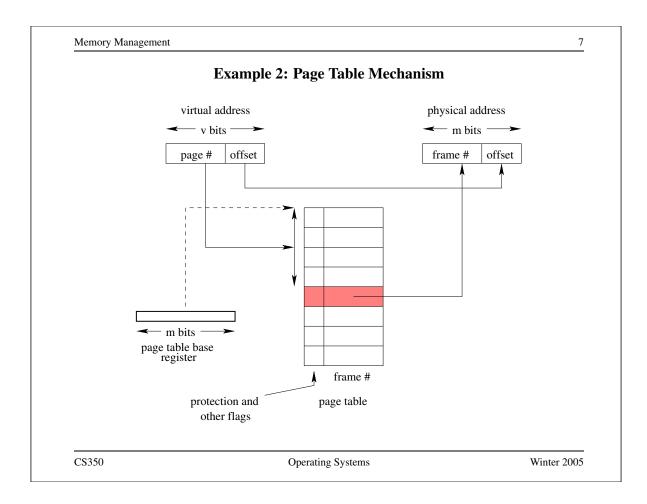

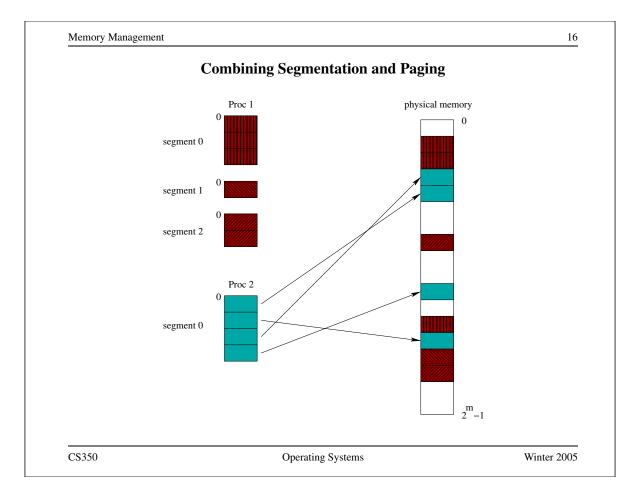

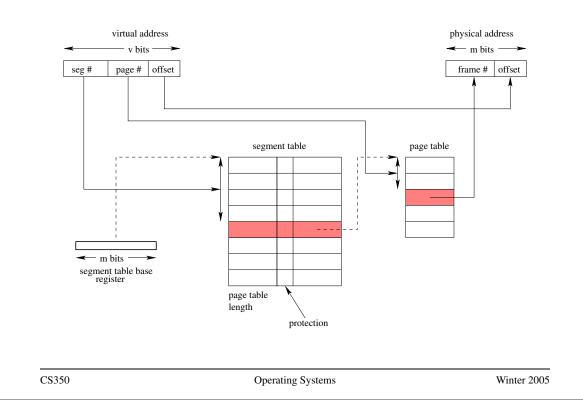

## **Example 2: Paging**

- Each virtual address space is divided into fixed-size chunks called pages

- The physical address space is divided into *frames*. Frame size matches page size.

- OS maintains a *page table* for each process. Page table specifies the frame in which each of the process's pages is located.

- At run time, MMU translates virtual addresses to physical using the page table of the running process.

- Properties

- simple physical memory management

- virtual address space need not be physically contiguous in physical space after translation.

CS350

Operating Systems

Winter 2005

5

| emory Manager |                                                                                |      |

|---------------|--------------------------------------------------------------------------------|------|

|               | Memory Protection                                                              |      |

| • ensure t    | hat each process accesses only the physical memory that its virtual            |      |

| address       | space is bound to.                                                             |      |

| – threa       | at: virtual address is too large                                               |      |

| – solut       | tion: MMU limit register checks each virtual address                           |      |

| * fo          | r simple dynamic relocation, limit register contains the maximum               |      |

| vi            | rtual address of the running process                                           |      |

|               | r paging, limit register contains the maximum page number of the nning process |      |

|               | U generates exception if the limit is exceeded                                 |      |

| • restrict t  | he use of some portions of an address space                                    |      |

| – exan        | nple: read-only memory                                                         |      |

| – appr        | oach (paging):                                                                 |      |

| * in          | clude read-only flag in each page table entry                                  |      |

| * M           | MU raises exception on attempt to write to a read-only page                    |      |

| 350           | Operating Systems Winter                                                       | 200, |

CS350

Operating Systems

Winter 2005

|                    | Speed of Address Translation                                                                                                    |                |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| • Executi operatio | on of each machine instruction may involve one, two                                                                             | or more memory |  |

| – one              | to fetch instruction                                                                                                            |                |  |

| – one              | or more for instruction operands                                                                                                |                |  |

| (for pag           | s translation through a page table adds one extra mem<br>ge table entry lookup) for each memory operation perf<br>ion execution | •              |  |

|                    | ple address translation through a page table can cut in<br>cution rate in half.                                                 | struction      |  |

|                    | re complex translation schemes (e.g., multi-level pagine expensive.                                                             | ng) are even   |  |

| Solution           | n: include a Translation Lookaside Buffer (TLB) in th                                                                           | ne MMU         |  |

| – TLE              | 3 is a fast, fully associative address translation cache                                                                        |                |  |

| – TLE              | 3 hit avoids page table lookup                                                                                                  |                |  |

| 50                 | Operating Systems                                                                                                               | Winter 200     |  |

|                                                | TLB                                                                                                                                          |                          |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| •                                              | 'LB contains a (page number,frame all of the page's protection bits, use                                                                     |                          |

| • If address translation page table is avoided | on can be accomplished using a TLI<br>ed.                                                                                                    | B entry, access to the   |

| memory - page nur                              | ch faster than a memory access. TLI<br>nbers of all entries are checked simi-<br>is typically small $(10^2 \text{ to } 10^3 \text{ entrie})$ | ultaneously for a match. |

| to the TLB, replaci                            | e through the page table, and add th<br>ng an existing entry if necessary. In<br>y the MMU. In a <i>software controlle</i>                   | a hardware controlled    |

| • On a context switch                          | h, the kernel must clear or invalidate                                                                                                       | e the TLB. (Why?)        |

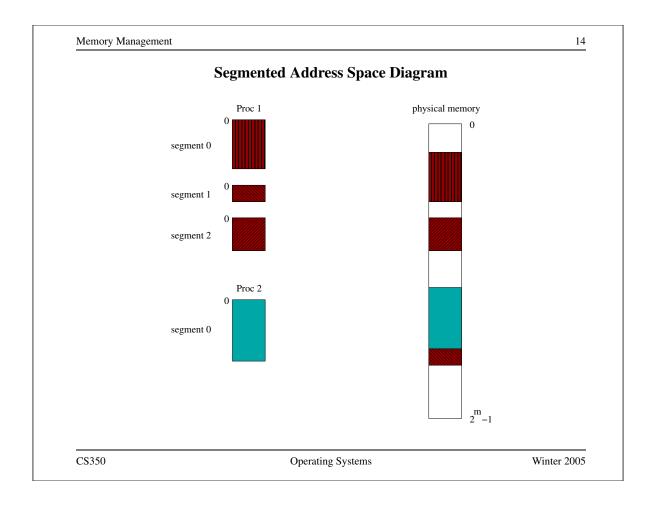

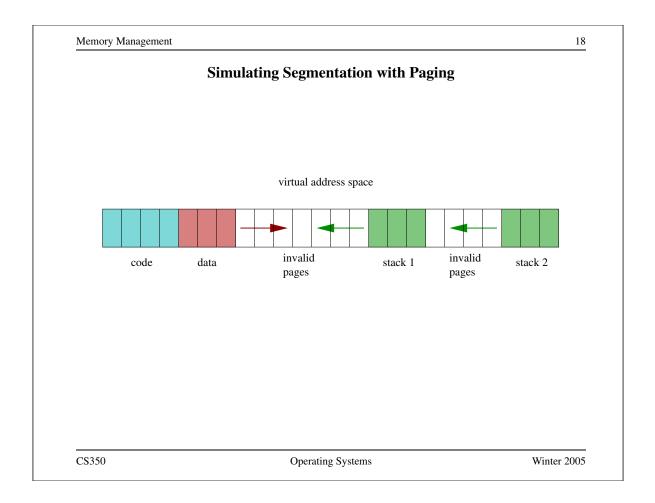

| Segmentation                            |                                                            |                         |

|-----------------------------------------|------------------------------------------------------------|-------------------------|

|                                         |                                                            |                         |

|                                         |                                                            |                         |

| • An OS that suppo<br>one address space | rts segmentation (e.g., Multics, OS/2)<br>to each process. | ) can provide more than |

| • The individual ad                     | dress spaces are called segments.                          |                         |

| • A logical address                     | consists of two parts:                                     |                         |

|                                         | (segment ID, address within segme                          | ent)                    |

| • Each segment:                         |                                                            |                         |

| <ul> <li>– can grow or sł</li> </ul>    | nrink independently of the other segm                      | ients                   |

| – has its own me                        | emory protection attributes                                |                         |

| • For example, prod                     | cess could use separate segments for c                     | code, data, and stack.  |

|                                         |                                                            |                         |

|                                         |                                                            |                         |

| CS350                                   | Operating Systems                                          | Winter 200              |

Memory Management

17